导入PCB与准备

- Altium Designer可以直接导出HyperLynx的文件,但是铺铜区域丢失。这里使用导出ODB++文件的方法,在文件->制造输出->ODB++ Files导出文件夹,在HyperLynx内可直接打开ODB++的文件夹作为项目。

- Allergo板图可以直接用HyperLynx打开导入。

导入时如果有些网络没有连接可能弹出警告”One or more nets are completely unrouted.”,直接选择No即可。

下面以STM32MP157评估板作为例子进行仿真,所需要的文件如下

- STM32MP15x IBIS file

- MB1272 Manufacturing files提取ODB++文件,或者选择下载MB1272 Board design project files打开PCB再进行导出

需要注意的时这里生成ODB++时Pin name有误,需要在components文件中清除前缀U*-,否则后续仿真导入模型时引脚名称对应不上 - 内存颗粒MT41J256M16TW的IBIS文件暂未找到,直接用HyperLynx自带的类似型号颗粒MT41J256M16HA的IBIS模型替代

仿真前配置

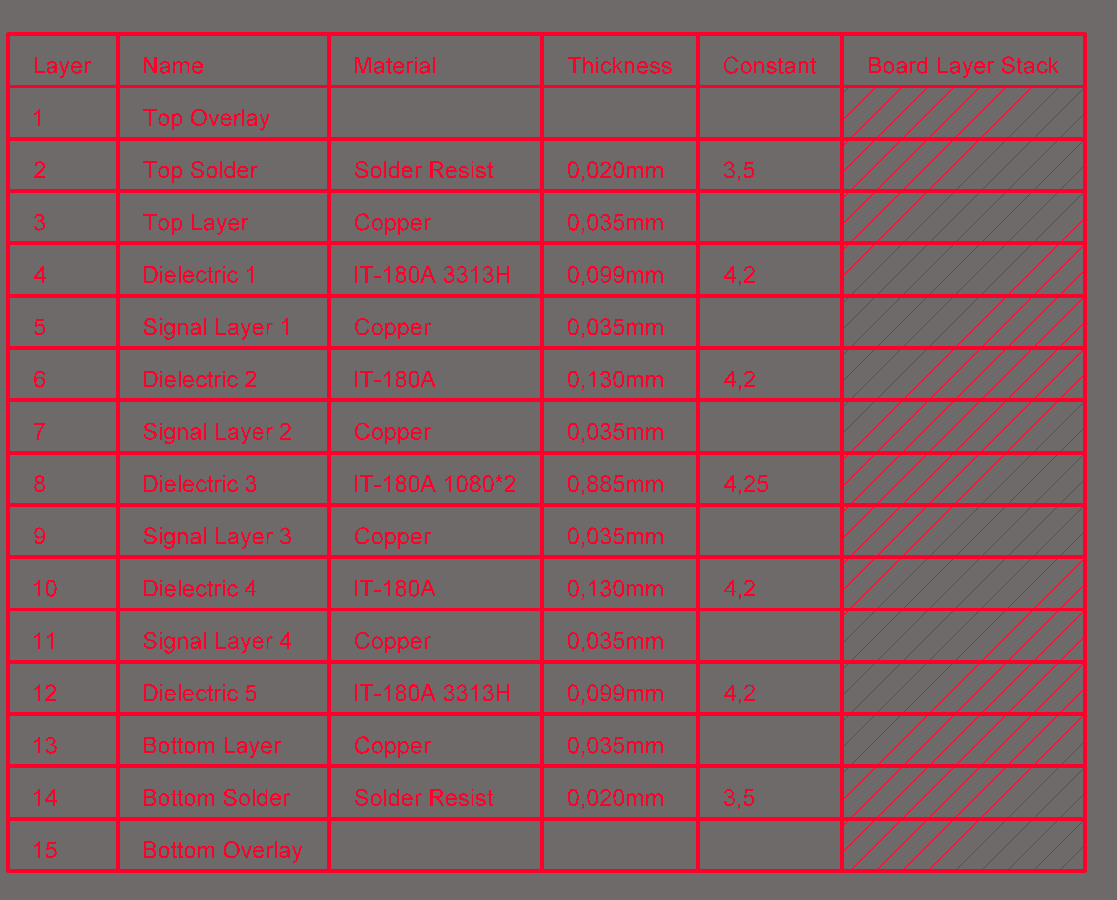

层叠设置

选择Setup->Stackup->Edit打开层叠设置。层叠设置一般在ODB++也有配置,这里按照上面PCB设计文件里给出的层叠表格的参数,把层叠厚度和介电常数填进去即可。铜层厚度的单位为oz或g,这里还需要换算一下1oz=35um。另外Type一栏的设置用于配置地平面和电源平面,按照原来的设计这块板第4层和第10层应该都是电源平面或地平面。实际应用中层叠参数一般在PCB生产厂家会给出。

配置电源网络

选择Setup->Power Supplies…打开电源网络配置。在Select supply nets下选择电源网络,在Edit supply voltages下输入电源电压。信号完整性仿真主要设置DDR的电源电压、VTT电压以及Vref电压.

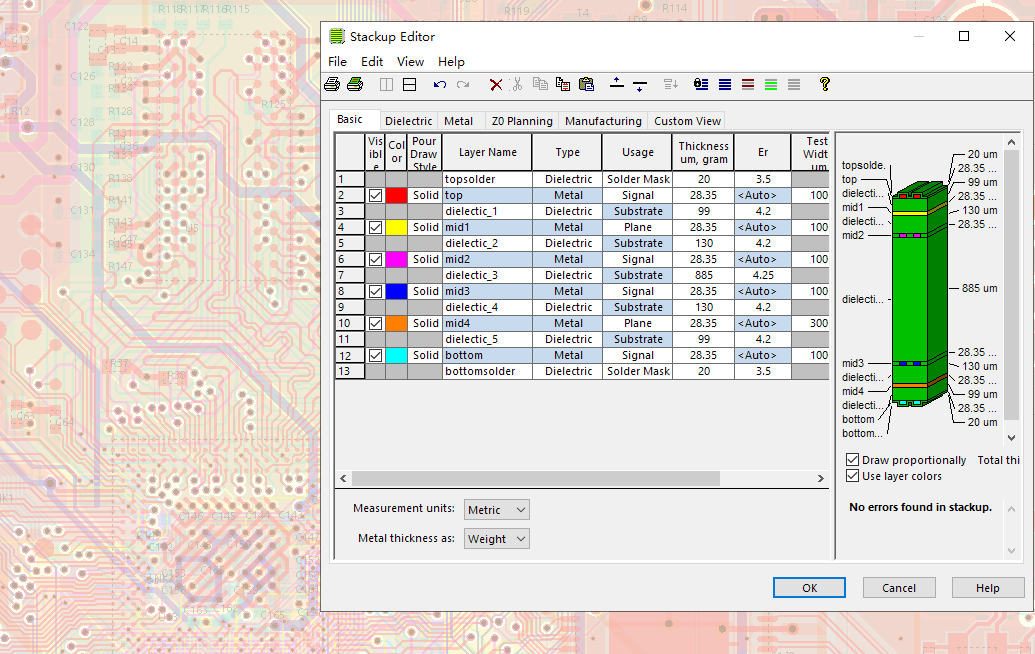

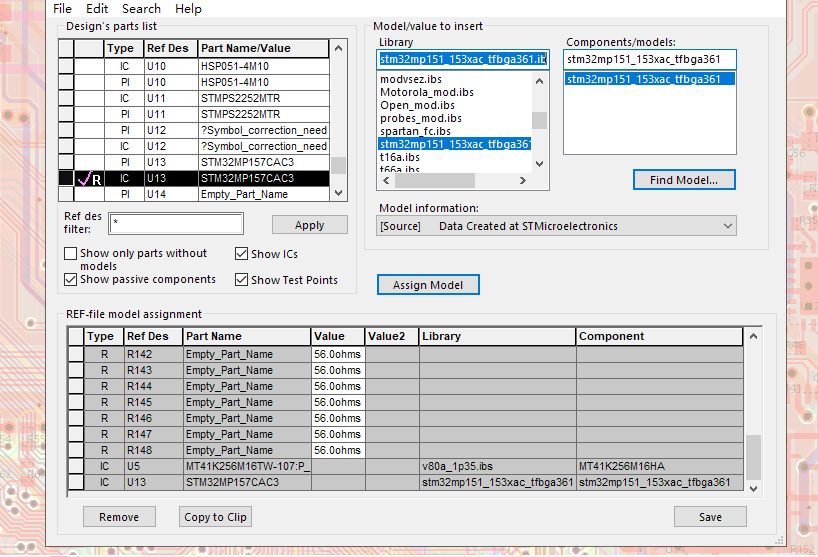

分配器件模型

首先需要将上面下载到的IBIS模型复制到项目目录下(ODB++文件夹所在的目录下),选择Models->Assign Models Values by Reference Desianator(.REF File)..按照器件分配模型。第一次打开可能会报错提示找不到ref文件,选择OK继续即可。

在Designer’s parts list下选择对应的器件,在右侧Library和Components/models列表中选择对应的模型文件和器件模型。一个器件可能有两种类型IC和PI,分别对应SI和PI,这里仅选择IC类型的器件分配模型。如果找不到在项目目录下的模型可以选择Models->Generate Model Finder Index刷新模型列表。STM32MP157的模型选择下载得到的IBIS模型,内存颗粒用系统自带的模型MT41J256M16HA。另外由于仿真需要,电路中的终端电阻也需要配置(具体看原理图中的DDR部分的电阻,主要有56欧姆和100欧姆),批量选择相同阻值的电阻在右侧填入阻值即可。

选择完成后点Assign分配,下方表格中会显示结果。分配完成后点Save保存分配结果。

运行仿真

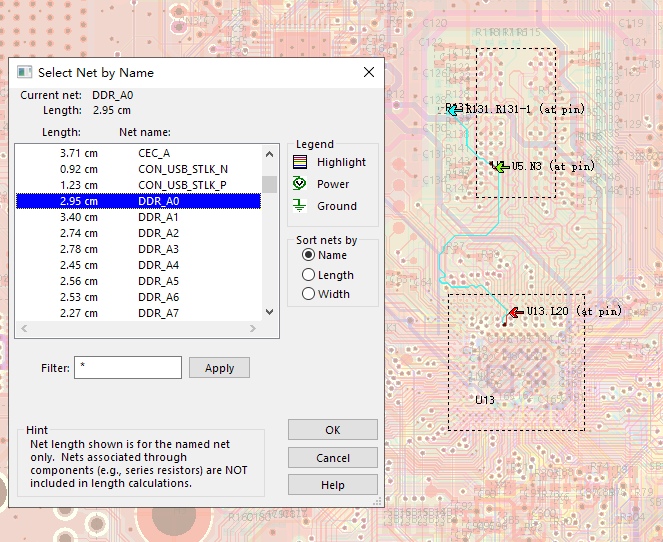

单网络仿真

选择Select->Net by Name for SI Analysis…在弹出的对话框中选择需要仿真的信号网络,这里选择DDR_A0为例。

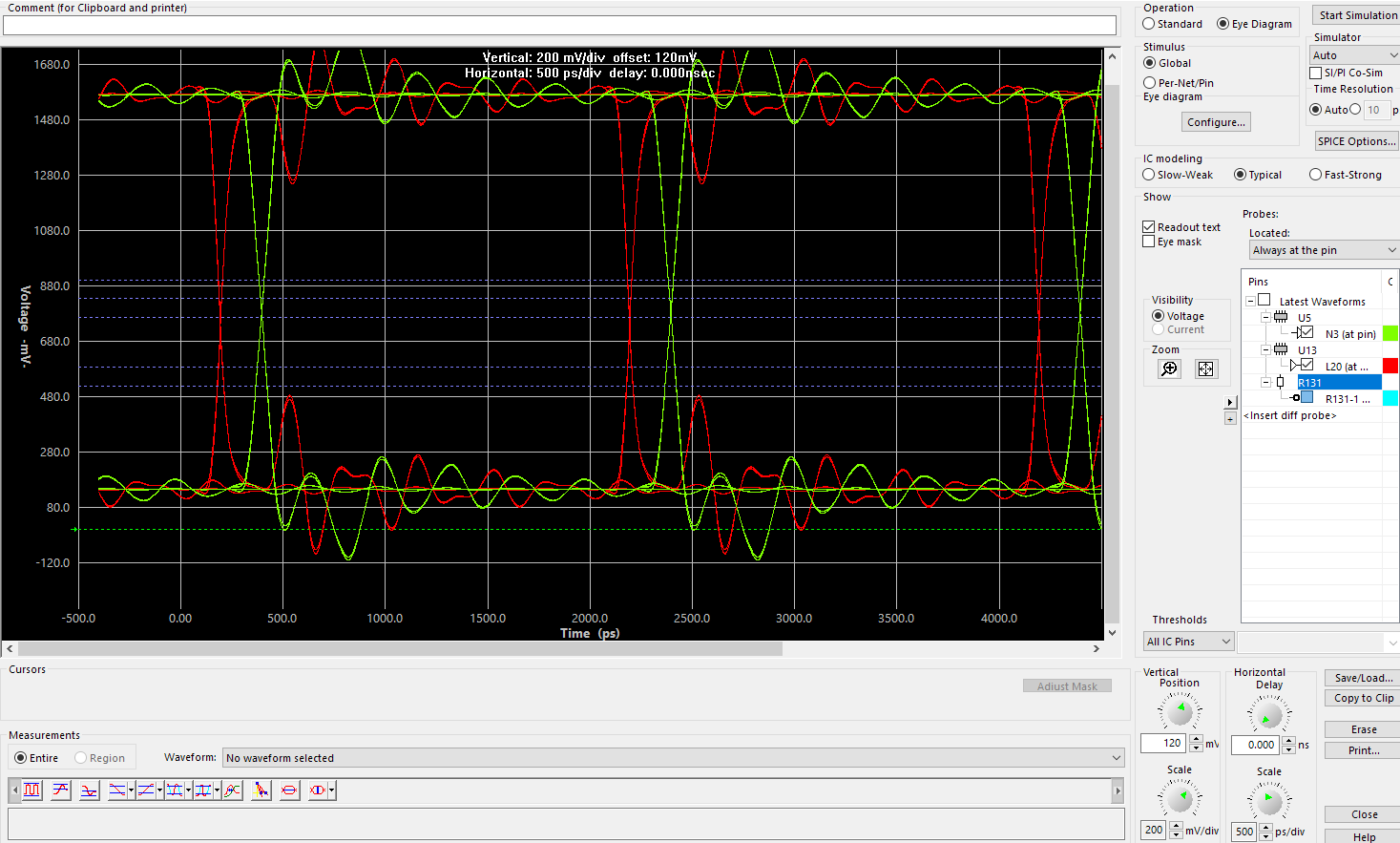

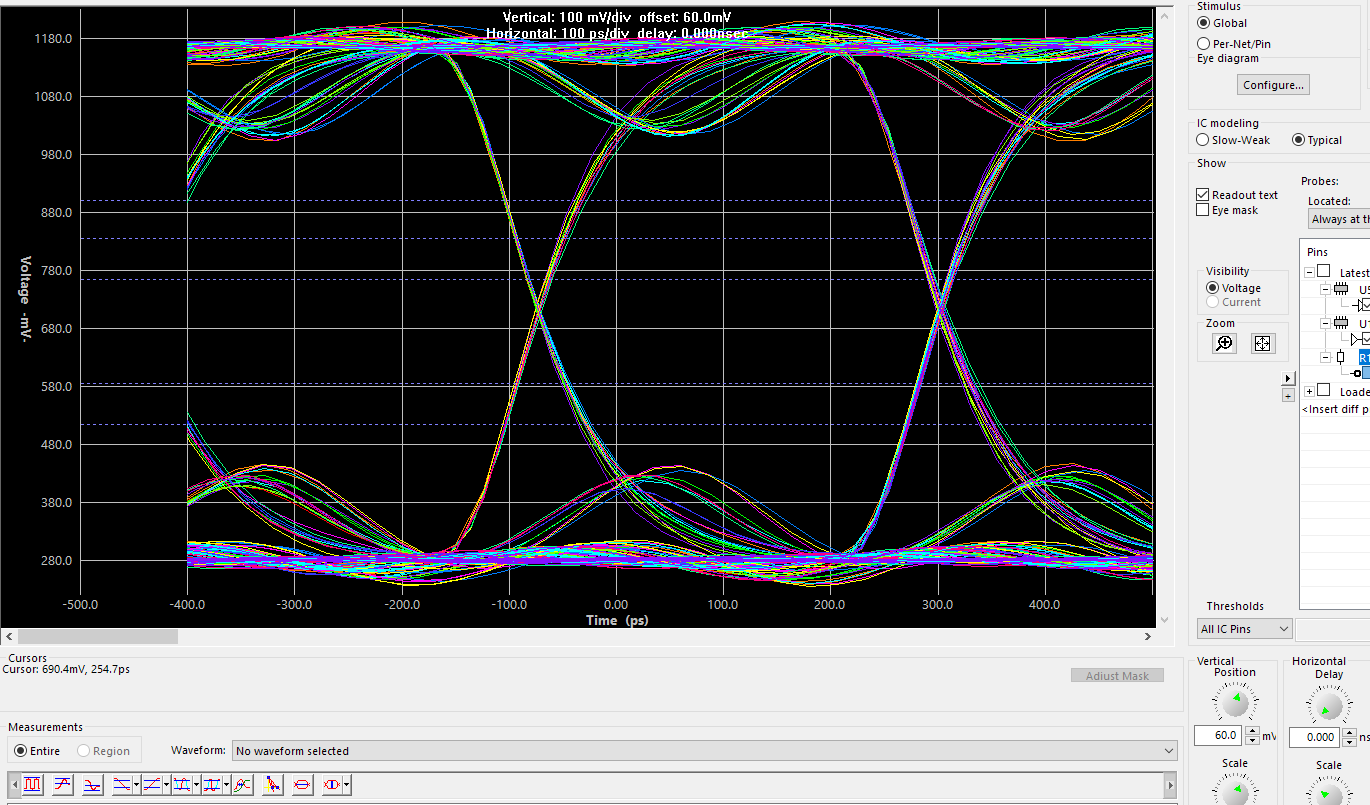

选择Models->Assign Models Values by Net…修改其中的引脚为驱动输出,使其能在该引脚上产生激励。选择Simulate SI->Run Interactive Simulation,在弹出对话框中可配置仿真参数。在右上角选择眼图,在Stimulus一栏点Configure配置输入激励。配置完成后勾选Probes即可启动仿真查看眼图波形。

DDR仿真

选择Simulate SI->Run DDRx Batch Simulation,在弹出对话框中按照说明一步一步进行即可。其中最为关键的几步如下,其他没有说明的步骤按照默认即可

- Initialization中配置DDR类型,这块板配置为DDR3 1.35V 1066MT/s

- Controller一步选择主机即STM32MP157

- DRAMs一步配置内存颗粒信息,这块板由于只有一个颗粒故Slots和Ranks均可以设为1

- IBIS Models一步如果之前分配的模型没有问题,再点击下一步即可

- DRAM Signals一步可以先选自动识别DDR信号,再在后面几步中分别确认网络是否正确

- ODT Models一步需要选择匹配的终端电阻,参考下面STM32MP1 Eval - Hyperlynx DDR Wizard Odt Model的回答设置。其中带有ODT+数字后缀的表示启用终端电阻并且其大小等于末尾数字的模型,信号的方向为输入,例如MSD_D3RP3L_ODT60表示DDR3L下ODT匹配电阻为60欧姆。而不带ODT的则为关闭终端电阻的驱动引脚模型,信号方向为输出。例如DQS_40_1066为在1066MT/s速率下输出阻抗40欧姆。

- IBIS Model Selectors选择无ODT下的引脚模型

- Simulation Options中的Select IC model corners选择Fast-strong

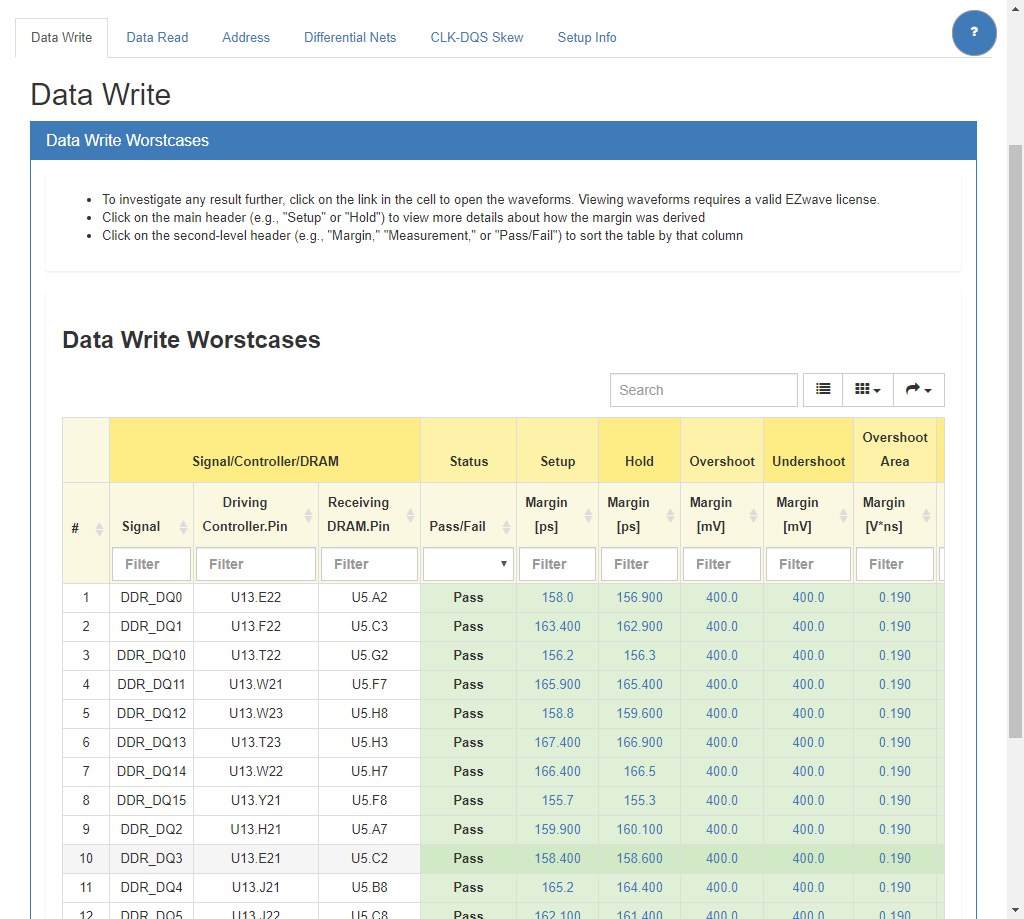

最后会生成一个.ddr的仿真配置文件,在仿真前也会要求保存。在最后一步Simulate中点Run Batch Simulation,在弹出对话框中点Run即可启动仿真。仿真结果会以网页形式显示,保存在项目目录下的一个文件夹里。运行该文件夹中的DDR_Report/report.bat可查看报告。

当然也可以再次选择Select->Net by Name for SI Analysis…打开波形查看器,右下方选择加载数据,选择仿真结果中的csv波形数据查看眼图

参考

- STM32MP15x CAD resources

- AN4803 - 在STM32 MCU和MPU上使用IBIS进行高速SI仿真以及使用HyperLynx®SI进行板级仿真,English

- STMicroelectronics Community - Horrible signal reflections and timing violations in DDR3L HyperLynx simulation of the STM32MP157 Discovery

- STM32MP1 Eval - Hyperlynx DDR Wizard Odt Model

- Signal Integrity Simulation - Getting started: Part 1 - Xilinx Support,Part 2

- Intel - DDR4 Simulation Guidelines